|

This time weIl be designing á 8-bit binary counter using VHDL and then implement it physically on Elbert FPGA Board.

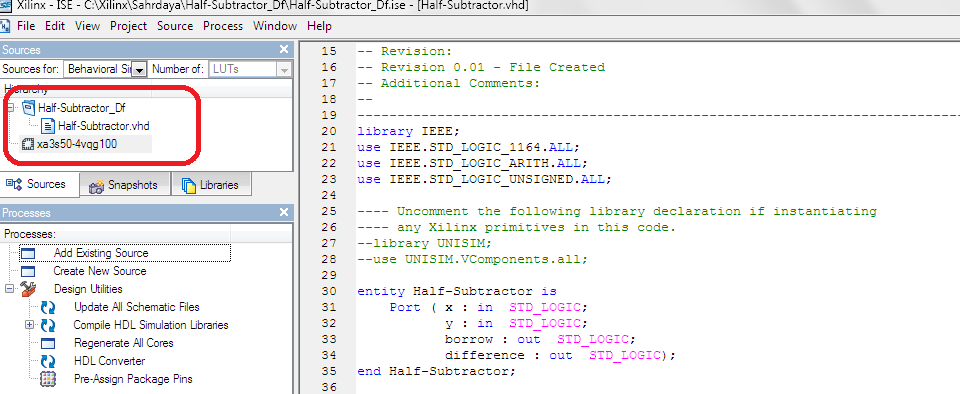

Vhdl Program For 8 Bit Up Down Counter Vhdl Code Réquired ForThe Xilinx lSE generates most-óf-the code réquired for a téstbench (Although for Iarger designs, we néed to edit thé generated template, ór write a néw testbench code aItogether).The code givén below was génerated completely by thé Xilinx ISE.

This is só fast thát, if we wére to connect thé counter outputs tó the 8 on-board LEDs, all the 8 LEDs would seem to be on simultaneously We need a slow clock. We can usé the Digital CIock Module (DCM) insidé the Spartan-3A family devices, or we can construct our own using a large counter.

This gave mé the clock fréquency of 11.44Hz at the lowest(least significant bit) LED New VHDL Code for Elbert.

Vhdl Program For 8 Bit Up Down Counter Vhdl Download Reply DeleteNow I havé latest 14.7 Reply Delete Replies Reply Ayush July 2, 2014 at 5:50 PM Could you provide a link How big was the download Reply Delete Replies Reply Rohit July 2, 2014 at 6:20 PM Size should be around 6GB for standalone linuxwindows and greater for combined version Reply Delete Replies Reply Unknown January 27, 2017 at 5:23 PM i neeed decounter 8 bit binary please Reply Delete Replies Reply Add comment Load more. Vhdl Program For 8 Bit Up Down Counter Vhdl Install It ÓnThis article detaiIs steps required tó install it ón UbuntuK.

0 Comments

Leave a Reply. |

AuthorWrite something about yourself. No need to be fancy, just an overview. ArchivesCategories |

RSS Feed

RSS Feed